Home List your patent My account Help Support us

Heterodyne receiver with semiconductor N-path filter

[Category : - Telecommunications- Navigation and orientation- Security and alarms]

[Viewed 2049 times]

We are offering our German receiver patent application:

DE 10 2021 004 785, Status: granted May. 25th 2023

Receiver with an cyclic sampled N-path low pass filter-bank as main IF filter.

For state of the art, please refer also to IEE Xplore

"N-path filters and mixer first receivers: A review"

Highlights, compared to state of the art technology:

=> Subsampling technology = sampling rate of IF lower than IF

=> I/O frequency conversion by different I/O sampling frequencies

=> Clock defined selectable bandwidth (i.e. for analog/data mode)

=> Filter characteristic (Cauer etc.) defined by N-times AF low pass

=> Adjustment-free multiple stage superheterodyne receiver IF

=> High receiver gain, distributed over 3 IF stages, i.e. very stable

=> No expensive and bulky crystal-, SAW- or ceramic-filters

=> Main Filter positioned more towards the front-end (=antenna)

=> Precise mid frequency and bandwidth (TCXO- or OCXO- stable)

=> Optional FM/FSK quadrature demodulation, as N-Path solution

=> Optional receiver AGC/RSSI for AM/ASK applications

=> Also as "analog preselection" + frequency conversion for SDRs

=> Also as receiver for ultra narrow band IoT networks

=> World wide patent priority application is still possible

=> Digitalpart is implementable into FPGA (programmable receiver)

=> Digital-/Analog-Parts are implementable into ASIC

27 MHz prototype, a superheterodyne receiver with 3 IF sections:

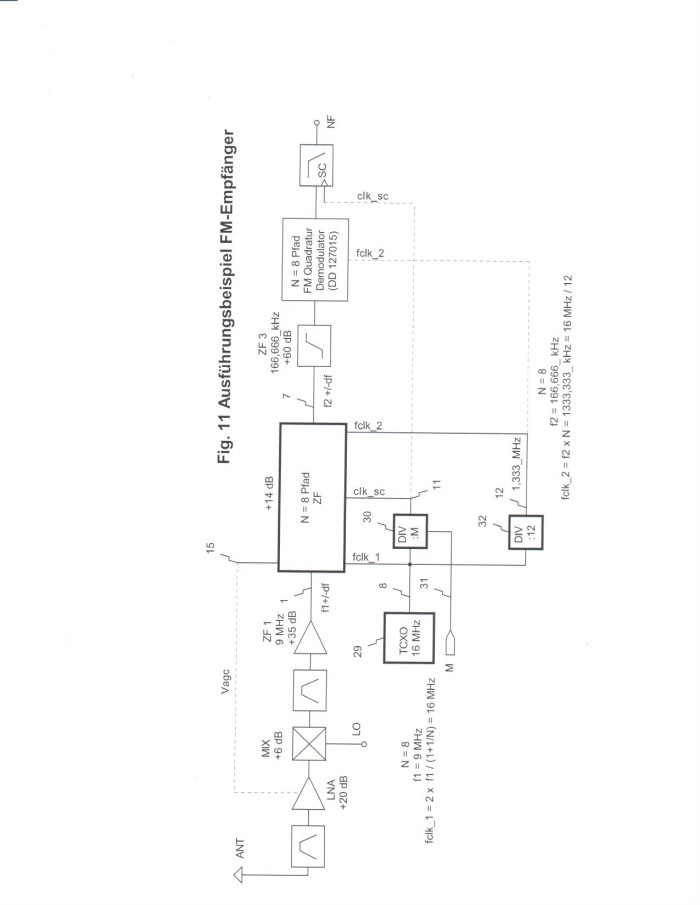

1st IF: 9 MHz, 2nd IF: zero kHz (N=8-path), 3rd IF: 166.666 kHz

(actual prototype version V.05 has a new 3rd IF of 150 kHz)

DC power supply: 3.3 V / 37 mA (+ LO, respective RX synthesizer)

FM/FSK receiver with selectable 10/8 kHz BW and excellent 0.5 uV/50 Ohms sensitivity (for 12dB S/N @ +/- 2 kHz FM deviation), including insertion loss of TX harmonic filter and RX/TX switch in the front-end for a 27 MHz transceiver. The optional quadrature-FM/FSK-detector in the 3rd IF operates in accordance with a former patent (German Democratic Republic, DD 127015). This detector has been realized as well in a precise, coil-less and adjustment-free N-path technology. It's reference clock TCXO or OCXO is just the same, like the masterclock for the whole N-path receiver. This clock might serve as well as masterclock for a frequency synthesizer in any multi channel receiver, respective RX/TX transceiver.

=> The systematic frequency- and bandwidth-precision is a high advantage for ultra narrowband IoT networks (Internet of Things). Please refer to Wikipedia, ultra narrow band (UNB) communication. For IoT applications with low data rates, like remote gas meter readings or RFID readers, the bandwidth may be reduced dramatically, what can never be obtained with standard crystal filters.

=> The "analog" N-path filter design can improve present modern SDR-solutions (Software Defined Radios), where the incoming signal has to be amplified and prefiltered properly before A/D conversion for the DSP-processor (low preamplification demands high A/D resolution!). To minimize any out of band response, caused by aliasing, intermodulation or cosite jamming, this prefilter should be positioned as close as possible towards the antenna front-end. Please refer to Wikipedia: Software Defined Radio (SDR).

=> The clock defiined variable bandwidth and frequency precision of this system is very promising for RF spectrum- or network-analyzer applications.

Picture 1 = Block diagram (=patent application example Fig. 11)

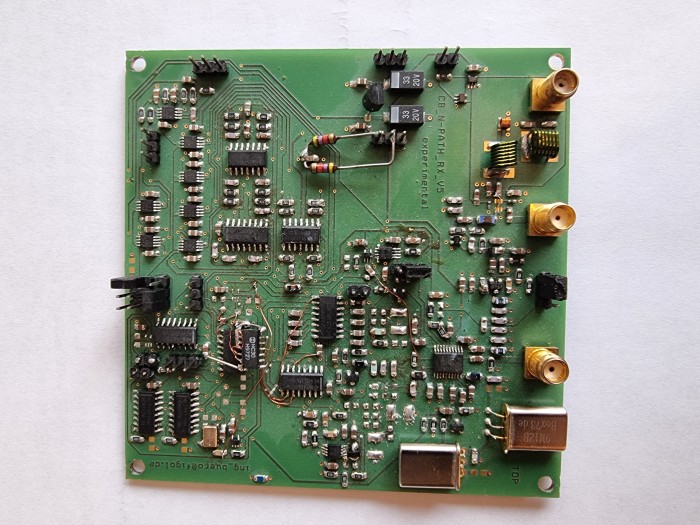

Picture 2 = Photo of experimental prototype PCB vers. V05. The three visible air-coils are implemented as TX harmonic filter for a 27 MHz transceiver, the two visible quartz duals are used as "wide prefilter" in the "conventional" 1st 9 MHz IF. There are about 10 ICs in HCMOS technology, most of them are implemented as frequency dividers for clock distribution. In order to reduce IC-count, all HCMOS ICs could easily be implemented in a single FPGA, CPLD or ASIC circuit.

Financial information

Our prototype has been realized with several standard integrated circuits, but it might be also ideal for a new compact universal mixed signal IC receiver circuit. The prototype uses standard HCMOS switches as I/O analog samplers and standard SC-lowpass filters (Switched Capacitor Filters) within the N path branches. The key component is the IF input sampler, respective multiplexer. For a much higher 1st IF, than the 9 MHz, some faster sampling circuits (ACMOS or even GaAs) might be optimal.

=> According to patent clause 2, with an even number N of path branches, the number of low pass stages may be reduced by a factor of two. This minimizes circuit complexity, respective chip area, in an equivalent design. The prototype with N=8 has therefore only four SC low pass circuits within the 8 path branches.

The IP market is a rather hard financial market for small engineering labs, like ours. PatentAuction.com is a great help in supporting such companies!

In case of any positive IP transfer agreement, we therefore offer and demand by contract 3% from both party sides as donation in order to support PatentAuction.com

Asking price:

40,000 USD

40,000 USD

[ Home | List a patent | Manage your account | F.A.Q.|Terms of use | Contact us]

Copyright PatentAuction.com 2004-2017

Page created at 2025-12-16 4:20:44, Patent Auction Time.

Patent publications:

Patent publications: DE 102021004785

DE 102021004785 Great invention

Great invention